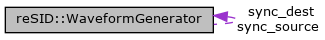

Collaboration diagram for reSID::WaveformGenerator:

Public Member Functions | |

| void | set_sync_source (WaveformGenerator *) |

| void | set_chip_model (chip_model model) |

| void | clock () |

| void | clock (cycle_count delta_t) |

| void | synchronize () |

| void | reset () |

| void | writeFREQ_LO (reg8) |

| void | writeFREQ_HI (reg8) |

| void | writePW_LO (reg8) |

| void | writePW_HI (reg8) |

| void | writeCONTROL_REG (reg8) |

| reg8 | readOSC () |

| short | output () |

| void | set_waveform_output () |

| void | set_waveform_output (cycle_count delta_t) |

Protected Member Functions | |

| void | clock_shift_register () |

| void | write_shift_register () |

| void | reset_shift_register () |

| void | set_noise_output () |

Protected Attributes | |

| const WaveformGenerator * | sync_source |

| WaveformGenerator * | sync_dest |

| reg24 | accumulator |

| bool | msb_rising |

| reg24 | freq |

| reg12 | pw |

| reg24 | shift_register |

| cycle_count | shift_register_reset |

| cycle_count | shift_pipeline |

| reg24 | ring_msb_mask |

| unsigned short | no_noise |

| unsigned short | noise_output |

| unsigned short | no_noise_or_noise_output |

| unsigned short | no_pulse |

| unsigned short | pulse_output |

| reg8 | waveform |

| reg12 | tri_saw_pipeline |

| reg12 | osc3 |

| reg8 | test |

| reg8 | ring_mod |

| reg8 | sync |

| reg12 | waveform_output |

| cycle_count | floating_output_ttl |

| chip_model | sid_model |

| unsigned short * | wave |

Static Protected Attributes | |

| static unsigned short | model_wave [2][8][1<< 12] |

| static unsigned short | model_dac [2][1<< 12] |

Friends | |

| class | Voice |

| class | SID |

Member Data Documentation

◆ model_dac

|

staticprotected |

Initial value:

= {

{0},

{0},

}

◆ model_wave

|

staticprotected |

Initial value:

= {

{

{0},

{0},

{0},

{0},

},

{

{0},

{0},

{0},

{0},

}

}

The documentation for this class was generated from the following files:

- wave.h

- wave.cc

1.8.18

1.8.18